ସିଲିକନ୍ ୱେଫର ସବଷ୍ଟ୍ରେଟରେ ସିଲିକନ୍ ପରମାଣୁର ଏକ ଅତିରିକ୍ତ ସ୍ତର ବୃଦ୍ଧି କରିବାର ଅନେକ ସୁବିଧା ଅଛି:

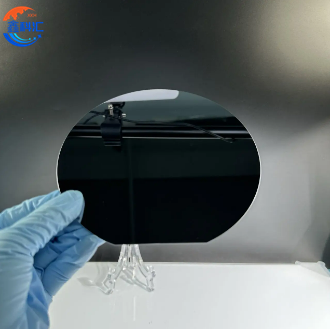

CMOS ସିଲିକନ୍ ପ୍ରକ୍ରିୟାରେ, ୱେଫର ସବଷ୍ଟ୍ରେଟରେ ଏପିଟାକ୍ସିଆଲ୍ ବୃଦ୍ଧି (EPI) ଏକ ଗୁରୁତ୍ୱପୂର୍ଣ୍ଣ ପ୍ରକ୍ରିୟା ପଦକ୍ଷେପ।

୧, ସ୍ଫଟିକ ଗୁଣବତ୍ତା ଉନ୍ନତ କରିବା

ପ୍ରାରମ୍ଭିକ ସବଷ୍ଟ୍ରେଟ୍ ତ୍ରୁଟି ଏବଂ ଅଶୁଦ୍ଧତା: ଉତ୍ପାଦନ ପ୍ରକ୍ରିୟା ସମୟରେ, ୱେଫର ସବଷ୍ଟ୍ରେଟ୍ରେ କିଛି ତ୍ରୁଟି ଏବଂ ଅଶୁଦ୍ଧତା ଥାଇପାରେ। ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରର ବୃଦ୍ଧି ସବଷ୍ଟ୍ରେଟ୍ରେ କମ୍ ତ୍ରୁଟି ଏବଂ ଅଶୁଦ୍ଧତାର ସାନ୍ଦ୍ରତା ସହିତ ଏକ ଉଚ୍ଚ-ଗୁଣବତ୍ତା ମନୋକ୍ରିଷ୍ଟାଲାଇନ୍ ସିଲିକନ୍ ସ୍ତର ଉତ୍ପାଦନ କରିପାରିବ, ଯାହା ପରବର୍ତ୍ତୀ ଉପକରଣ ନିର୍ମାଣ ପାଇଁ ଅତ୍ୟନ୍ତ ଗୁରୁତ୍ୱପୂର୍ଣ୍ଣ।

ସମାନ ସ୍ଫଟିକ ଗଠନ: ଏପିଟାକ୍ସିଆଲ୍ ବୃଦ୍ଧି ଏକ ସମାନ ସ୍ଫଟିକ ଗଠନ ସୁନିଶ୍ଚିତ କରେ, ଯାହା ଶସ୍ୟ ସୀମା ଏବଂ ସବଷ୍ଟ୍ରେଟ୍ ସାମଗ୍ରୀରେ ତ୍ରୁଟିର ପ୍ରଭାବକୁ ହ୍ରାସ କରେ, ଏହାଦ୍ୱାରା ୱେଫରର ସାମଗ୍ରିକ ସ୍ଫଟିକ ଗୁଣବତ୍ତା ଉନ୍ନତ ହୁଏ।

2, ବୈଦ୍ୟୁତିକ କାର୍ଯ୍ୟଦକ୍ଷତା ଉନ୍ନତ କରିବା।

ଡିଭାଇସର ବୈଶିଷ୍ଟ୍ୟଗୁଡ଼ିକୁ ଅପ୍ଟିମାଇଜ୍ କରିବା: ସବଷ୍ଟ୍ରେଟ୍ ଉପରେ ଏକ ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତର ବୃଦ୍ଧି କରି, ଡୋପିଂ ସାନ୍ଦ୍ରତା ଏବଂ ସିଲିକନର ପ୍ରକାରକୁ ସଠିକ୍ ଭାବରେ ନିୟନ୍ତ୍ରଣ କରାଯାଇପାରିବ, ଯାହା ଡିଭାଇସର ବୈଦ୍ୟୁତିକ କାର୍ଯ୍ୟଦକ୍ଷତାକୁ ଅପ୍ଟିମାଇଜ୍ କରିଥାଏ। ଉଦାହରଣ ସ୍ୱରୂପ, MOSFETs ଏବଂ ଅନ୍ୟାନ୍ୟ ବୈଦ୍ୟୁତିକ ପାରାମିଟରଗୁଡ଼ିକର ଥ୍ରେସହୋଲ୍ଡ ଭୋଲଟେଜକୁ ନିୟନ୍ତ୍ରଣ କରିବା ପାଇଁ ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରର ଡୋପିଂକୁ ସୂକ୍ଷ୍ମ ଭାବରେ ଆଡଜଷ୍ଟ କରାଯାଇପାରିବ।

ଲିକେଜ୍ କରେଣ୍ଟ ହ୍ରାସ କରିବା: ଏକ ଉଚ୍ଚ-ଗୁଣବତ୍ତା ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରର ତ୍ରୁଟି ଘନତା କମ୍ ଥାଏ, ଯାହା ଡିଭାଇସଗୁଡ଼ିକରେ ଲିକେଜ୍ କରେଣ୍ଟ ହ୍ରାସ କରିବାରେ ସାହାଯ୍ୟ କରେ, ଏହା ଦ୍ୱାରା ଡିଭାଇସର କାର୍ଯ୍ୟଦକ୍ଷତା ଏବଂ ନିର୍ଭରଯୋଗ୍ୟତା ଉନ୍ନତ ହୁଏ।

3, ବୈଦ୍ୟୁତିକ କାର୍ଯ୍ୟଦକ୍ଷତା ଉନ୍ନତ କରିବା।

ବୈଶିଷ୍ଟ୍ୟ ଆକାର ହ୍ରାସ କରିବା: ଛୋଟ ପ୍ରକ୍ରିୟା ନୋଡଗୁଡ଼ିକରେ (ଯେପରିକି 7nm, 5nm), ଡିଭାଇସଗୁଡ଼ିକର ବୈଶିଷ୍ଟ୍ୟ ଆକାର ସଙ୍କୁଚିତ ହେବାରେ ଲାଗିଛି, ଯାହା ପାଇଁ ଅଧିକ ପରିଷ୍କୃତ ଏବଂ ଉଚ୍ଚ-ଗୁଣବତ୍ତା ସାମଗ୍ରୀ ଆବଶ୍ୟକ ହୁଏ। ଏପିଟାକ୍ସିଆଲ୍ ଅଭିବୃଦ୍ଧି ପ୍ରଯୁକ୍ତିବିଦ୍ୟା ଏହି ଚାହିଦାଗୁଡ଼ିକୁ ପୂରଣ କରିପାରିବ, ଉଚ୍ଚ-କାର୍ଯ୍ୟଦକ୍ଷତା ଏବଂ ଉଚ୍ଚ-ଘନତା ସମନ୍ୱିତ ସର୍କିଟ୍ ନିର୍ମାଣକୁ ସମର୍ଥନ କରି।

ବ୍ରେକଡାଉନ୍ ଭୋଲଟେଜ ବୃଦ୍ଧି କରିବା: ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରଗୁଡ଼ିକୁ ଅଧିକ ବ୍ରେକଡାଉନ୍ ଭୋଲଟେଜ ସହିତ ଡିଜାଇନ୍ କରାଯାଇପାରିବ, ଯାହା ଉଚ୍ଚ-ଶକ୍ତି ଏବଂ ଉଚ୍ଚ-ଭୋଲଟେଜ ଡିଭାଇସ୍ ନିର୍ମାଣ ପାଇଁ ଗୁରୁତ୍ୱପୂର୍ଣ୍ଣ। ଉଦାହରଣ ସ୍ୱରୂପ, ବିଦ୍ୟୁତ୍ ଡିଭାଇସ୍ଗୁଡ଼ିକରେ, ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରଗୁଡ଼ିକ ଡିଭାଇସ୍ର ବ୍ରେକଡାଉନ୍ ଭୋଲଟେଜକୁ ଉନ୍ନତ କରିପାରିବ, ସୁରକ୍ଷିତ କାର୍ଯ୍ୟ ପରିସରକୁ ବୃଦ୍ଧି କରିପାରିବ।

୪, ପ୍ରକ୍ରିୟା ସୁସଙ୍ଗତତା ଏବଂ ବହୁସ୍ତରୀୟ ଗଠନ

ବହୁସ୍ତରୀୟ ଗଠନ: ଏପିଟାକ୍ସିଆଲ୍ ଅଭିବୃଦ୍ଧି ପ୍ରଯୁକ୍ତିବିଦ୍ୟା ସବଷ୍ଟ୍ରେଟ୍ଗୁଡ଼ିକରେ ବହୁସ୍ତରୀୟ ଗଠନର ଅଭିବୃଦ୍ଧି ପାଇଁ ଅନୁମତି ଦିଏ, ବିଭିନ୍ନ ସ୍ତରଗୁଡ଼ିକରେ ବିଭିନ୍ନ ଡୋପିଂ ସାନ୍ଦ୍ରତା ଏବଂ ପ୍ରକାର ରହିଥାଏ। ଏହା ଜଟିଳ CMOS ଡିଭାଇସ୍ ନିର୍ମାଣ ଏବଂ ତ୍ରି-ପରିମାଣୀୟ ସମନ୍ୱୟକୁ ସକ୍ଷମ କରିବା ପାଇଁ ଅତ୍ୟନ୍ତ ଲାଭଦାୟକ।

ସୁସଙ୍ଗତତା: ଏପିଟାକ୍ସିଆଲ୍ ଅଭିବୃଦ୍ଧି ପ୍ରକ୍ରିୟା ବିଦ୍ୟମାନ CMOS ଉତ୍ପାଦନ ପ୍ରକ୍ରିୟା ସହିତ ଅତ୍ୟନ୍ତ ସୁସଙ୍ଗତ, ଯାହା ପ୍ରକ୍ରିୟା ଲାଇନ୍ରେ ଗୁରୁତ୍ୱପୂର୍ଣ୍ଣ ପରିବର୍ତ୍ତନ ବିନା ବର୍ତ୍ତମାନର ଉତ୍ପାଦନ କାର୍ଯ୍ୟପ୍ରବାହରେ ସମନ୍ୱିତ କରିବା ସହଜ କରିଥାଏ।

ସାରାଂଶ: CMOS ସିଲିକନ୍ ପ୍ରକ୍ରିୟାରେ ଏପିଟାକ୍ସିଆଲ୍ ଅଭିବୃଦ୍ଧିର ପ୍ରୟୋଗ ମୁଖ୍ୟତଃ ୱାଫର ସ୍ଫଟିକ ଗୁଣବତ୍ତା ବୃଦ୍ଧି କରିବା, ଡିଭାଇସ୍ ବୈଦ୍ୟୁତିକ କାର୍ଯ୍ୟଦକ୍ଷତାକୁ ଅପ୍ଟିମାଇଜ୍ କରିବା, ଉନ୍ନତ ପ୍ରକ୍ରିୟା ନୋଡଗୁଡ଼ିକୁ ସମର୍ଥନ କରିବା ଏବଂ ଉଚ୍ଚ-କାର୍ଯ୍ୟଦକ୍ଷତା ଏବଂ ଉଚ୍ଚ-ଘନତା ସମନ୍ୱିତ ସର୍କିଟ୍ ଉତ୍ପାଦନର ଚାହିଦା ପୂରଣ କରିବା ଲକ୍ଷ୍ୟରେ ରହିଛି। ଏପିଟାକ୍ସିଆଲ୍ ଅଭିବୃଦ୍ଧି ପ୍ରଯୁକ୍ତିବିଦ୍ୟା ସାମଗ୍ରୀ ଡୋପିଂ ଏବଂ ଗଠନର ସଠିକ୍ ନିୟନ୍ତ୍ରଣ ପାଇଁ ଅନୁମତି ଦିଏ, ଯାହା ଡିଭାଇସ୍ଗୁଡ଼ିକର ସାମଗ୍ରିକ କାର୍ଯ୍ୟଦକ୍ଷତା ଏବଂ ନିର୍ଭରଯୋଗ୍ୟତାକୁ ଉନ୍ନତ କରିଥାଏ।

ପୋଷ୍ଟ ସମୟ: ଅକ୍ଟୋବର-୧୬-୨୦୨୪